x86架构-预备知识

阅读数:90 评论数:0

跳转到新版页面分类

硬件/嵌入式

正文

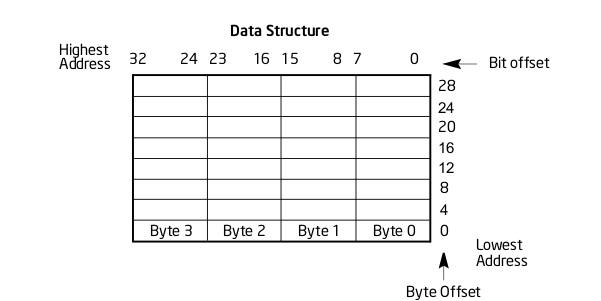

1、位和字节的顺序

Intel 64和IA-32处理器是小端模式(最低有效字节存储在低地址位置)。

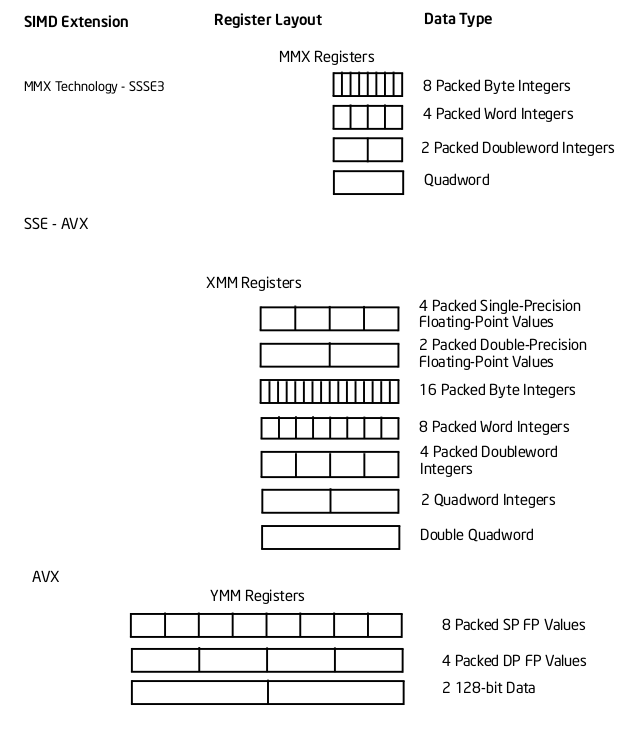

2、SIMD指令(single-instruction multiple-data)

单指令多数据,主要由6个扩展实现:

(1)MMX 技术

(2)SSE扩展

(3)SSE2扩展

(4)SSE3扩展

(5)支持流SIMD扩展3

(6)SSE4

每个扩展都包括一组指令。SIMD的整数操作可以使用64位的MMX或128位的XMM寄存器,SIMD浮点操作使用128位的XMM寄存器。

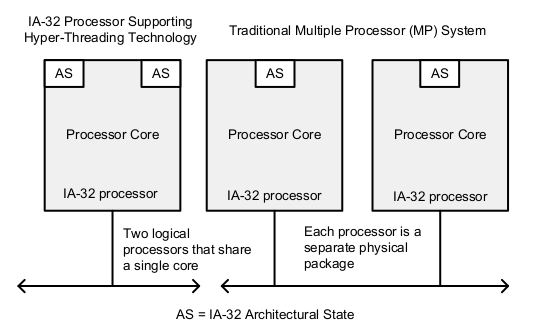

3、Intel的超线程技术

主要用来提高IA-32处理的性能,可以通过共享执行资源来使单处理器同时执行多个线程。在架构上,通过使用逻辑处理器,每个逻辑处理器有自己的data register、segment register、control register、debug register和大部分的MSR,同时还有自己的APIC(Advanced programmable interrupt controller)。

4、cpu模式

IA-32有三个基本的操作模式 :

(1)保护模式

可以保护性的执行实地址模式的8086软件,是一种多任务环境,也称为虚拟8086模式。

(2)实地址模式

(3)系统管理模式(SMM)

处理器会使用一个特殊的地址空间。

Intel 64还有2个子模式:

(1)兼容模式

可以直接执行16位或32位的程序。

(2)64位模式

使用64位的线性址。

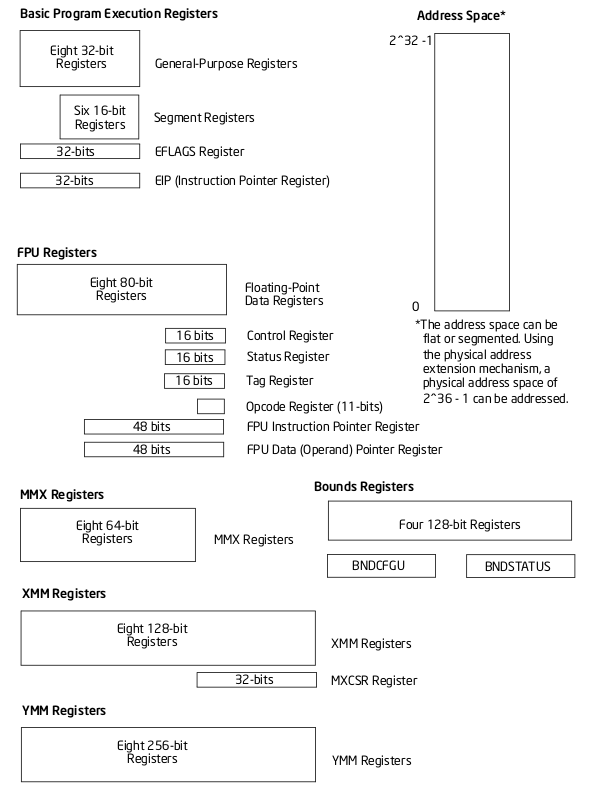

5、IA-32中指令的基本执行环境

(1)地址空间

程序可以使用的线性地址最大到4GBytes($2^32 bytes$),物理地址最大可到64GBytes($2^36 bytes$)

(2)基本程序执行寄存器

8个通用寄存器,6个段寄存器,EFLAGS寄存器,EIP(instruction pointer)寄存器。

(3)x87 FPU 寄存器

8个x87 FPU 数据寄存器,x87 FPU控制寄存器,状态寄存器,x87 FPU 指令寄存器,x87 FPU操作数寄存器,x87 FPU tag寄存器,x87 FPU opcode寄存器。

(4)MMX寄存器

8个MMX寄存器

(5)XMM寄存器

8个XMM数据寄存器和MXCSR寄存器

(6)YMM寄存器

(7)Bounds 寄存器

BND0~BND3

(8)BNDCFGU 和BNDSTATUS

(9)Stack

另外还有扩展:

(1)I/O 端口

(2)控制寄存器

5个,从CR0~CR4

(3)内存管理寄存器

GDTR,IDTR,task 寄存器

(4)调试寄存器

DR0~DR7

(5)MTTRs(Memory type range registers)

(6)MSRs(Model-specific registers)

(7)Machine check registers

(8)性能监控计数器

6、内存组织

操作系统通过cpu来访问内存的。

IA-32的内存模型

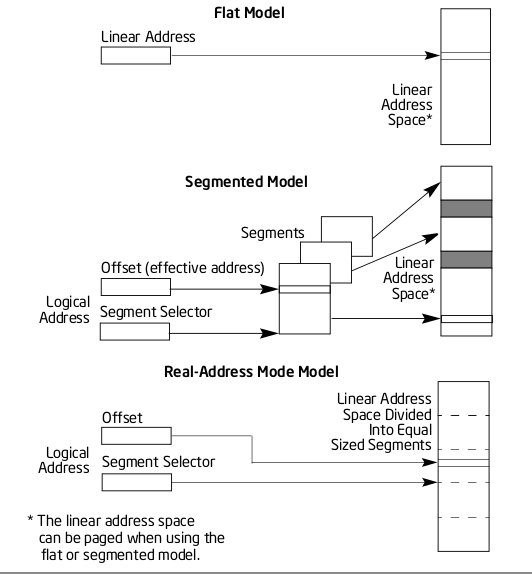

(1)扁平内存模型(flat)

一个连续地址空间,称为线性地址。

(2)段内存模型

内存被分为一组独立的地址空间,称为段。代码、数据和栈包含在不同的段中。在IA-32中,最多有16383个段,每个段可以有4Gbytes空间大小。段模式可以增强程序和系统的可信性。

(3)真实地址内存模式

最大的线性地址空间是$2^20 bytes$,程序或操作系统使用是由段组成的地址空间,每个段大小为64Kbytes。

分页和虚拟内存

IA-32架构的分页机制,是把线性地址转换成物理地址。

(1)PAE(Physical Address Extension),使定位的物理地址大于4GBytes

(2)PSE(Page Size Extensions),线性地址物理地址时使用4Mbytes页。